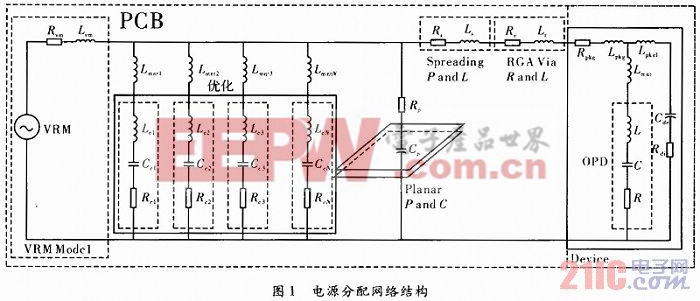

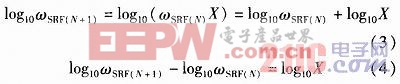

随着芯片制造工艺的发展及应用需求的增加,其集成度慢慢的升高。因此,在高速高密度芯片内就会不可避免地产生电源噪声,而其供电引脚也会引入大量外部电路中的电源噪声,这些电源噪声对电路设计的影响已成为高速PCB设计的瓶颈。 当稳压器输出阻抗超出目标阻抗时,就需要采取一定的措施降低整个网络的有效阻抗,一般是通过添加去耦电容器解决这一个问题。 文中以电源分配网络的结构为基础,为解决电源完整性(Power Integrity,PI)问题,以达到使电路板上的电源分配网络能为芯片提供纯净的电源,去耦电容器种类与个数的选择环节至关重要。文中主要介绍了去耦电容器种类选择的算法,以及提出的基于谐振频率电容器种类的选择算法。 (1)Big“V”法。是利用容值相同的多个电容器并联生成的低阻抗来降低PDN(Power Distribution Net)阻抗。通过持续不断的增加某一容值电容器的个数达到设计目标。由于Big“V”方法应用的前提是不考虑平面并联谐振,通常选用较大容值的电容器。Dr.Howard Johnson建议考虑选择所提供的容值最大的电容器。 (2)Flat Response与Decade Methods。两种方法是利用不一样容值的多个电容器并联生成的低阻抗以降低阻抗特性。 陶瓷电容器,特别是小容值的电容器,通常表现出很高的Q值:每个电容器在SRF处的ESR比jL小得多。当给定目标阻抗和频段时,应充分的利用这一些器件的高Q值,经过控制ESR而不是jL来设计去耦网络。 要设计出一个较为平坦的PDN阻抗特性,这些容值递减的电容器分别所需的个数会随ESR值增多。假设网络中所有电容器即具有相同的封装,也具有相同的安装电感,这时它们的SRF有以下规律 其中,X可理解为相邻两个电容器自谐振频率问的比例关系。从而,Flat Response中的X=1.47,Decade Methods中的X=3.16。转化为对数坐标 由于这两种方法中X均为常数,从而由式(4)能够准确的看出,所选容值的自谐振频率在对数坐标下是等间隔分布的。